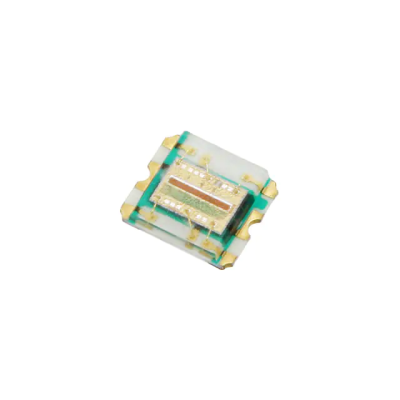

APDS-9301-020

Part Number: APDS-9301-020

Manufacturer: Broadcom / Avago

Description: Ambient Light Sensors Digital Light Sensor (I2C 3.3V)

Shipped from: Shenzhen/HK Warehouse

Stock Available: Check with us

ICRFQ.com - Electronic Components Distributor in China Since 2003

Part Number: APDS-9301-020

Manufacturer: Broadcom / Avago

Description: Ambient Light Sensors Digital Light Sensor (I2C 3.3V)

Shipped from: Shenzhen/HK Warehouse

Stock Available: Check with us

| Datasheet | |

|---|---|

| Category | Sensors, Transducers |

| Family | Optical Sensors – Ambient Light, IR, UV Sensors |

| Manufacturer | Broadcom Limited |

| Series | – |

| Packaging | Cut Tape (CT) |

| Part Status | Active |

| Type | Ambient |

| Wavelength | 640nm |

| Proximity Detection | No |

| Output Type | I2C |

| Voltage – Supply | 2.7 V ~ 3.6 V |

| Operating Temperature | -30°C ~ 85°C |

| Mounting Type | Surface Mount |

| Package / Case | 6-SMD, No Lead |

| Supplier Device Package | 6-Pin ChipLED |

The APDS-9301 is an I2C-compatible digital light sensor that directly converts light intensity into digital signals. One visible light (broadband) photodiode and one infrared light (IR) photodiode make up each unit. Each channel’s irradiance is represented thanks to two integrating analog-to-digital converters (ADCs) digitally. This digital signal can be fed into a microcontroller, which will then use an empirical formula to estimate the human eye’s response and calculate the illuminance (ambient light intensity) in lux.

The currents from the APDS-9301’s channel 0 and channel 1 photodiodes are integrated by two analog-to-digital converters (ADC). After the cycle, the channel 0 and channel 1 data registers contain the conversion result from combining the two channels simultaneously. Data transfers are protected from invalid data reading by employing a double-buffering technique. When the handoff is complete, the device will begin the next integration cycle.

The APDS-9301 is controlled and interfaced with via a series of registers that may be accessed via a serial interface using only two wires. This allows full access to the device’s control operations and output data. The serial port can communicate in Fast-Mode with an I2C bus. The APDS-9301 includes a pin for externally selecting one of three slave addresses (ADDR SEL).

The Send and Write protocols are just a string of bytes in their most basic form. To indicate a COMMAND byte to the APDS-9301, set the MSB of the byte to 1. The register select address, seen in Table 2, is formed by the lower four bits of the COMMAND byte. This address determines the location for the subsequent byte (or bytes) received. Any Receive Byte requests made to the APDS-9301 will result in a response with the contents of the register defined by the stored register chosen address.

A serial interface-accessible command register and sixteen registers (three reserved) control and monitor the APDS-9301. These registers show ADC conversion results. These registers are responsible for a wide variety of control operations.

The address of the target register that will be used for subsequent read and write operations is specified by the command register. The Send Byte protocol must first be utilized to configure the COMMAND register. Table 3 outlines the contents of the command register, which total eight bits. When the power is turned on, the command register will be set to 00h by default.

The registers for the interrupt threshold are where you’ll put the high and low values that the comparison function will use to cause an interrupt to be generated. Channel 0’s output triggers an interrupt if its value falls below or is equal to the low threshold. The interrupt pin will be asserted if the value produced by channel 0 goes above the high point. The lower interrupt threshold’s low byte and high byte are stored in THRESHLOWLOW and THRESHLOWHIGH. The upper interrupt threshold is stored in the registers THRESHHIGHLOW and THRESHHIGHHIGH, with the low and high bytes shown accordingly. A 16-bit threshold value is calculated by adding the high and low bytes from each pair of registers. On power up, the interrupt threshold registers are initially set to 00h.

In the APDS-9301, the INTERRUPT register governs all of the interrupt features. The APDS-9301 supports standard interrupts in the level format. The PERSIST bit field regulates when interrupts can occur. If the value is 0, an interruption will happen after each integration cycle regardless of the threshold. When set to 1, integration is halted after one period that falls outside the threshold window. Only if the value stays beyond the threshold window for N successive integration cycles does an interrupt occur, where N is a positive integer between 2 and 15. It takes about 4 seconds; for instance, if N is ten and the integration time is 402 milliseconds. When an Interrupt level is set, a signal is sent whenever the result of the most recent conversion falls outside the threshold range. This active-low interrupt will stay asserted until the CLEAR bit in the COMMAND register is written.

Data from each ADC channel is represented by a pair of 16-bit numbers stored in separate registers. Registers DATA0LOW and DATA0HIGH for ADC channel 0 stores the low and high bytes of the channel 0 ADC value, respectively. The ADC value for channel one is stored in two registers named DATA1LOW and DATA1HIGH. All channel data registers are set at power on to 00h, the read-only value.

The window’s dimensions and design must meet specific requirements to ensure the APDS-9301’s performance. The minimum window size in front of the photo light sensor must not impair the APDS9301’s angular response. The specified minimum dimension ensures a ±35° light reception cone.

Light pipes or guides can reduce the window size. Total internal reflection focuses light in a cylindrical light pipe or light guide made of transparent plastic. Every optical window loses 8% of power owing to review (4% on each side) and energy in the plastic substance; hence the window should be as thin as feasible.

Contact ICRFQ, your one-stop shop for electronic sourcing components in China, if you require further information or like to place an order for the APDS-9301-020. We will work hard to ensure you get the best possible products at affordable prices.

WhatsApp us