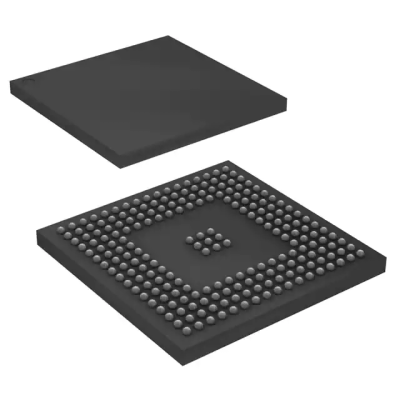

AT91SAM9X25-CU

Part Number: AT91SAM9X25-CU

Manufacturer: Microchip Technology / Atmel

Description: Microprocessors – MPU BGA GRN IND TMP MRLA

Shipped from: Shenzhen/HK Warehouse

Stock Available: Check with us

ICRFQ.com - Electronic Components Distributor in China Since 2003

Part Number: AT91SAM9X25-CU

Manufacturer: Microchip Technology / Atmel

Description: Microprocessors – MPU BGA GRN IND TMP MRLA

Shipped from: Shenzhen/HK Warehouse

Stock Available: Check with us

| Datasheet | |

|---|---|

| Category | Integrated Circuits (ICs) |

| Family | Embedded – Microcontrollers |

| Manufacturer | Atmel |

| Series | SAM9X |

| Packaging | Tray |

| Part Status | Active |

| Core Processor | ARM9? |

| Core Size | 16/32-Bit |

| Speed | 400MHz |

| Connectivity | CAN, EBI/EMI, Ethernet, I2C, LIN, MMC, SPI, SSC, UART/USART, USB |

| Peripherals | DMA, POR, PWM, WDT |

| Number of I/O | 105 |

| Program Memory Size | 64KB (64K x 8) |

| Program Memory Type | ROM |

| EEPROM Size | – |

| RAM Size | 32K x 8 |

| Voltage – Supply (Vcc/Vdd) | 0.9 V ~ 1.1 V |

| Data Converters | A/D 12x10b |

| Oscillator Type | Internal |

| Operating Temperature | -40°C ~ 85°C (TA) |

| Package / Case | 217-LFBGA |

| Supplier Device Package | 217-BGA (15×15) |

The SAM9X25 belongs to the 400 MHz ARM926EJ-STM embedded microprocessor series from Atmel® | SMART. This MPU has a variety of networking and connection peripherals tailored for commercial uses in areas including building automation, gateways, and healthcare.

Two Controller Area Network (CAN) interfaces that are 2.0A/B compatible and two 10/100 Mbps Ethernet MACs that are IEEE Std 802.3 compatible are also included in the SAM9X25. A soft modem that only supports the Conexant SmartDAA line driver is among the other communication interfaces, along with two HS SDCard/SDIO/MMC interfaces, HS USB Device and Host, FS USB Host, SPIs, I2S, USARTs, TWIs, and 10-bit ADC.

The SAM9X25 has a 10-layer bus matrix along with 2 x 8 central DMA channels, dedicated DMAs for the high-speed connection peripherals, and DMAs to enable uninterrupted data flow with the least amount of processor overhead. Specifically designed circuitry for MLC/SLC NAND Flash with integrated ECC up to 24 bits is included in the External Bus Interface, along with controllers for 4-bank and SDRAM/LPSDRAM, 8-bank DDR2/LPDDR, static memories, and other memory types. With a 217-ball BGA package and 0.8 mm ball pitch, the SAM9X25 is offered.

ARM® Thumb® Processor ARM926EJ-STM operating at up to 400 MHz @ 1.0V +/- 10%

Memory Management Unit, 16 Kbytes of Data Cache, and 16 Kbytes of Instruction Cache

A single internal ROM embedding bootstrap function of 64 kilobytes: Boot from a serial data flash drive, NAND flash, SDCard, or data flash. Programmable sequence.

Single-cycle access to a single 32-Kbyte internal SRAM at system speed

A large bandwidth DDR SDR SDRAM Multi-port Controller (DDRSDRC)

32-bit External Bus Interface with 4-bank and 8-bank LPDDR, SDR/LPSDR, Static Memories MLC/SLC 8-bit NAND Controller, and up to 24-bit Programmable Multi-bit Error Correcting Code

Reset Controller, Reset Cells, Periodic Interval Timer, Shutdown Controller, Watchdog Timer, and Real-Time

Launch Mode. Choose the Remap Command option.

Fast 12 MHz and Internal Low Power 32 kHz RC Oscillators

Selectable 12 MHz Oscillator and 32768 Hz Low-power Oscillator

two PLLs: one for the system and one at 480 MHz that is USB-optimized. High Tempo

AHB Bus Matrix with 12 32-bit layers for high bandwidth transfers

Use a double peripheral bridge with a dedicated programmable clock for optimal performance.

Advanced Interrupt Controller (AIC), two dual-port 8-channel DMA Controllers (DMAC), and Debug Unit (DBGU)

Two External Clock Signals That Are Programmable

With four 32-bit battery backup registers, the shutdown controller

Generator of timepieces and power management controller

Operating with a very slow clock and having software-programmable power optimization capabilities

High-Speed USB Device, High-Speed USB Host, and Full-Speed USB Host with Dedicated On-Chip Transceiver

Two Ethernet MAC controllers at 10/100 Mbps (EMAC)

two hosts for high-speed memory cards

a pair of CAN controllers

Parallel Serial Interfaces with Two Master/Slave Devices (SPI)

Two 32-bit 3-channel timer/counters (TC)

there is one synchronized serial controller (SSC)

four 16-bit PWM channels in one controller

Two-wire Interfaces Three (TWI)

Two UARTs, four USARTs, and one DBGU

Device Software Modem (SMD)

Protected Registers to Write

Four 32-bit Parallel Input/Output Controllers

Input Change Interrupt Capability on Each I/O Line, optional Schmitt trigger input

Pull-up and pull-down resistor, Synchronous Output , Individually Programmable Open-drain.

217-ball BGA, pitch 0.8 mm

| TYPE | DESCRIPTION |

| Category | Integrated Circuits (ICs)

Embedded Microprocessors |

| Mfr | Microchip Technology |

| Series | SAM9X |

| Package | Tray |

| Product Status | Active |

| Core Processor | ARM926EJ-S |

| Number of Cores/Bus Width | 1 Core, 32-Bit |

| Speed | 400MHz |

| Co-Processors/DSP | – |

| RAM Controllers | LPDDR, LPDDR2, DDR2, DDR, SDR, SRAM |

| Graphics Acceleration | No |

| Display & Interface Controllers | – |

| Ethernet | 10/100Mbps (2) |

| SATA | – |

| USB | USB 2.0 (3) |

| Voltage – I/O | 1.8V, 2.5V, 3.0V, 3.3V |

| Operating Temperature | -40°C ~ 85°C (TA) |

| Security Features | – |

| Package / Case | 217-LFBGA |

| Supplier Device Package | 217-LFBGA (15×15) |

| Additional Interfaces | CAN, EBI/EMI, I²C, MMC/SD/SDIO, SPI, SSC, UART/USART |

| Base Product Number | AT91SAM9 |

The AHB Bus Matrix, which implements the Advanced High-performance Bus (AHB) for its Master and Slave interfaces with extra capabilities, performs a first-level address decoding.

16 banks of 256 Mbytes make up the 4 Gbyte address space after decoding. Banks 1 through 6 are connected to the external chip selects, EBI NCS0 through EBI NCS5, by the EBI, which is where they are directed. Bank 0 is set aside for internal memory address, and the second decoding level offers 1 Mbyte of interior memory space.

Access to the Advanced Peripheral Bus is provided by Bank 15, which is set aside for peripherals (APB). Other sections are unoccupied; therefore, entering their results can abort the master making the request.

Thanks for reading. If you like this article, please explore the rest of our website for more great content like this one and learn more. If you have any questions about this article, please leave them in the comment section below, and we will do our best to respond to them.

If you need information or want to order AT91SAM9X25-CU, contact us here at ICRFQ, your leading electronic components in china, and we will ensure you get the best product at the best price.

WhatsApp us