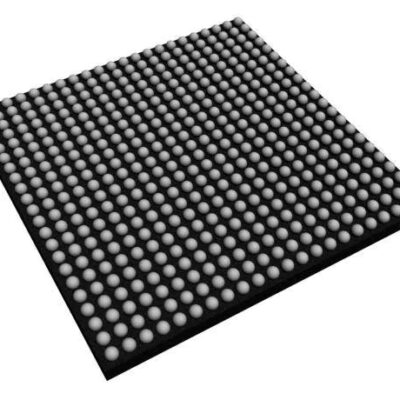

EP4CE55F23C8N

Part Number: EP4CE55F23C8N

Manufacturer: Intel

Description: IC FPGA 324 I/O 484FBGA

Shipped from: Shenzhen/HK Warehouse

Stock Available: Check with us

ICRFQ.com - Electronic Components Distributor in China Since 2003

Part Number: EP4CE55F23C8N

Manufacturer: Intel

Description: IC FPGA 324 I/O 484FBGA

Shipped from: Shenzhen/HK Warehouse

Stock Available: Check with us

| Datasheet | |

|---|---|

| Category | Integrated Circuits (ICs) |

| Family | Embedded – FPGAs (Field Programmable Gate Array) |

| Manufacturer | Altera |

| Series | Cyclone? IV E |

| Part Status | Active |

| Number of LABs/CLBs | 3491 |

| Number of Logic Elements/Cells | 55856 |

| Total RAM Bits | 2396160 |

| Number of I/O | 324 |

| Number of Gates | – |

| Voltage – Supply | 1.15 V ~ 1.25 V |

| Mounting Type | Surface Mount |

| Operating Temperature | 0°C ~ 85°C (TJ) |

| Package / Case | 484-BGA |

| Supplier Device Package | 484-FBGA (23×23) |

When Cyclone IV devices are integrated into a system, the system determines the parameters against which they are evaluated for rating. You must take into consideration the operating requirements outlined in this chapter to keep the performance and dependability of Cyclone IV devices at their highest possible level. Devices based on the Cyclone IV platform can be purchased in commercial, industrial, extended industrial, and automotive grades.

Cyclone IV E devices provide speed grades of –6 (the fastest), –7, –8, –8L, and –9L for commercial devices, –8L speed grades for industrial devices, and –7-speed grades for extended industrial and automotive devices. For commercial devices, Cyclone IV GX offers the –6 (fastest) speed grade, as well as –7 and –8-speed grades; for industrial devices, the –7-speed grade is available.

There are two core voltage options available for the Cyclone IV E devices: 1.0 and 1.2 V. A prefix of ‘L’ is added to the speed grade of Cyclone IV E devices when the core voltage is 1.0 V.

| EU RoHS | Compliant |

| ECCN (US) | 3A991 |

| Part Status | Active |

| HTS | 8542.39.00.01 |

| Automotive | No |

| PPAP | No |

| Family Name | Cyclone® IV E |

| Process Technology | 60nm |

| User I/Os | 324 |

| Number of I/O Banks | 8 |

| Operating Supply Voltage (V) | 1.2 |

| Logic Elements | 55856 |

| Number of Multipliers | 154 (18×18) |

| Program Memory Type | SRAM |

| Embedded Memory (Kbit) | 2340 |

| Total Number of Block RAM | 260 |

| Device Logic Units | 55856 |

| Number of Global Clocks | 20 |

| Device Number of DLLs/PLLs | 4 |

| JTAG Support | Yes |

| Dedicated DSP | 154 |

| PCIe | 1 |

| Programmability | Yes |

| Programmability Support | No |

| Number of Look-up Table Input | 4 |

| Copy Protection | No |

| In-System Programmability | No |

| Speed Grade | 8 |

| Differential I/O Standards | B-LVDS|HSTL|LVPECL|LVDS|RSDS|SSTL |

| Single-Ended I/O Standards | LVTTL|LVCMOS|PCI|PCI-X|SSTL|HSTL |

| External Memory Interface | DDR SDRAM|DDR2 SDRAM|QDRII+SRAM |

| Minimum Operating Supply Voltage (V) | 1.16 |

| Maximum Operating Supply Voltage (V) | 1.24 |

| I/O Voltage (V) | 1.2|1.5|1.8|2.5|3|3.3 |

| Minimum Operating Temperature (°C) | 0 |

| Maximum Operating Temperature (°C) | 85 |

| Supplier Temperature Grade | Commercial |

| Packaging | Tray |

| Tradename | Cyclone |

| Mounting | Surface Mount |

| Package Height | 1.75 |

| Package Width | 23 |

| Package Length | 23 |

| PCB changed | 484 |

| Standard Package Name | BGA |

| Supplier Package | FBGA |

| Pin Count | 484 |

| Lead Shape | Ball |

are used to define the most extreme conditions that can be encountered while operating Cyclone IV devices. The values were derived from the results of experiments carried out with the device and theoretical modeling of the mechanisms that cause breakage and damage. Under these circumstances, one should not assume that the device is working correctly in its intended capacity.

During transitions, the magnitude of input signals may overshoot to the voltage or undershoot to –2.0 V for less than 20 nanoseconds and currents with a magnitude of fewer than 100 milliamperes (mA).

In this part, the specifications for Cyclone IV devices are broken down into categories like I/O leakage current, pin capacitance, on-chip termination (OCT) tolerance, and bus hold. The Circulating Current of Supply The minimum current that must be pulled from the power supply pins is known as the device supply current requirement, and it can serve as a point of reference for planning the amount of power required. It is recommended that you use the early power estimator (EPE) that is based on Excel to obtain the supply current estimations for your design because these currents fluctuate widely depending on the resources utilized.

After the source driving, it has either entered the high impedance state or been removed entirely, and the bus-hold will keep its last valid logic state. Within user mode, a switch may be activated to enable bus hold for each individual I/O pin. When in configuration mode, the hold function for the bus is always turned off.

Cyclone IV devices include support for Schmitt trigger input on various pins, including TDI, TMS, TCK, nSTATUS, nCONFIG, nCE, CONF DONE, and DCLK. Hysteresis is introduced to the input signal through a Schmitt trigger, which results in better noise immunity, particularly for signals with a slow edge rate.

The tables that follow provide information regarding the input voltage sensitivity (VIH and VIL), output voltage (VOH and VOL), and current driving characteristics (IOH and IOL) for the various I/O standards that Cyclone IV devices can handle.

To get an estimate of the power required for a design, use the following methods:

Before creating the device, the interactive, Excel-based EPE is utilized to gain a magnitude estimate of the device’s power output. After the place-and-route process is finished, the Quartus II PowerPlay power analyzer can produce more accurate estimations by considering the design’s particulars. The PowerPlay power analyzer can use a combination of user-entered, simulation-derived, and estimated signal activity, which, when combined with precise circuit models, can result in very accurate power estimates.

This section details Cyclone IV core performance parameters and peripheral blocks for commercial-grade devices. Depending on the situation, these traits might be marked as either Preliminary or Final.

The outcomes of simulations, data from the process, and any other known parameters are used to provide preliminary characteristics. In the top-right-hand corner of each table is the word “Preliminary,” inscribed in italics.

The final statistics have been determined based on the characterization and testing of natural silicon. These statistics represent the device’s actual performance when subjected to the worst-case scenario for the silicon process, voltage, and junction temperature. The tables that have been finalized do not include any designations.

This part discusses the performance of the peripherals, including high-speed I/O and the interface for external memory. I/O performance supports various system interfaces, including the high-speed I/O interface, the external memory interface, and the PCI/PCI-X bus interface, among others. I/Os that adhere to the SSTL-18 Class I termination standard can reach the maximum DDR2 SDRAM interface rates specified. I/Os that adhere to general-purpose I/O standards, such as 3.3-, 3.0-, 2.5-, 1.8-, or 1.5-LVTTL/LVCMOS, can achieve a typical interface frequency of 200 MHz even when a load of 10 pF is present.

To determine the timing of I/O operations, use the following methods:

I/O timing based on Excel delivers pin timing performance for every device density and speed grade. In most cases, the data is utilized before the construction of the FPGA to estimate the timing budget as a component of the link timing analysis. After the place-and-route phase of the design is over, the Quartus II timing analyzer delivers I/O timing data that is more exact and precise since it is based on the particulars of the design.

Contact ICRFQ, your one-stop shop for purchasing electronic components in China, if you need further information or wish to place an order for the EP4CE55F23C8N. We will work hard to ensure you get the best possible products at affordable prices.

WhatsApp us