TFP401AIPZPRQ1

Part Number: TFP401AIPZPRQ1

Manufacturer: Texas Instruments

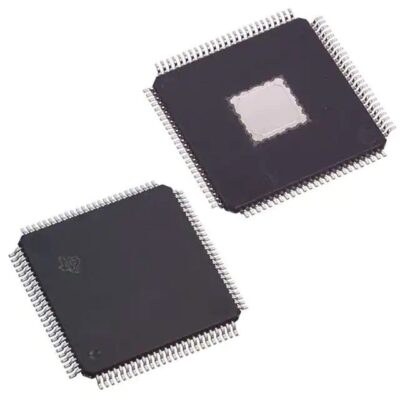

Description: IC RECEIVER 0/3 100HTQFP

Shipped from: Shenzhen/HK Warehouse

Stock Available: Check with us

ICRFQ.com - Electronic Components Distributor in China Since 2003

Part Number: TFP401AIPZPRQ1

Manufacturer: Texas Instruments

Description: IC RECEIVER 0/3 100HTQFP

Shipped from: Shenzhen/HK Warehouse

Stock Available: Check with us

| Datasheet | |

|---|---|

| Category | Integrated Circuits (ICs) |

| Family | Interface – Drivers, Receivers, Transceivers |

| Manufacturer | Texas Instruments |

| Series | Automotive, AEC-Q100 |

| Packaging | Tape & Reel (TR) |

| Part Status | Active |

| Type | Receiver |

| Protocol | PanelBus? |

| Number of Drivers/Receivers | 0/3 |

| Duplex | – |

| Receiver Hysteresis | – |

| Data Rate | – |

| Voltage – Supply | 3 V ~ 3.6 V |

| Operating Temperature | -40°C ~ 85°C |

| Mounting Type | Surface Mount |

| Package / Case | 100-TQFP Exposed Pad |

| Supplier Device Package | 100-HTQFP (14×14) |

The Texas Instruments TFP401A-Q1 device is a complete family of end-to-end DVI 1.0-compliant solutions and a TI PanelbusTM flat-panel display product. The TFP401A-Q1 primarily aims for desktop LCDs and digital projectors, although it can be used in any design where a high-speed digital interface is required. Regarding screen resolutions, the TFP401A-Q1 device can handle everything from 1080p to WUXGA in 24-bit true-color pixels.

Ground bounce can be adjusted with more precision because it works with both TFT and DSTN displays, supports time-staggered pixel outputs, and can be set to drive either one or two pixels per clock. The PowerPAD innovative packaging technique achieves its class’s lowest ground inductance, smallest footprint, and highest power dissipation. The TFP401A-Q1 is a low-power, low-noise, high-speed digital interface solution that blends Panelbus circuit innovation with TI’s state-of-the-art 0.18-m EPIC-5TM CMOS process technology and TI PowerPAD package technology.

Receiving and decoding TMDS-encoded RGB pixel data streams is the function of the TFP401A-Q1 device, which is a digital receiver for TMDS that complies with the digital visual interface (DVI) and is used in digital flat-panel display systems. A TMDS-compatible transmitter can be found within the host of a digital display system, which is often a personal computer or workstation. This transmitter accepts 24-bit pixel data along with the relevant control signals. The host encodes the data and control signals into a high-speed, low-voltage differential serial bit stream (suitable for transmission via a twisted-pair cable), which is then sent to a display device.

To decode the serial bit stream and produce the same 24-bit pixel data and control signals generated by the host, the display device, which is often a flat-panel monitor, needs a TMDS-compatible receiver like the TI TFP401A-Q1 device. After being decoded, the data are in a form that may be used appropriately for direct application to the flat-panel drive circuitry to generate a picture on display. Because the distance between the host and display can be as much as five meters or more, the serial transmission of the pixel data is recommended whenever possible. To support contemporary display resolutions up to UXGA, you will need a receiver with a large bandwidth and a high tolerance for jitter and skew.

The gadget only sends one of two possible TMDS characters for a pixel at any time. To approximate a dc balance of the transmission line, the transmitter keeps track of the number of ones and zeros that have already been delivered and sends the character with the fewest transitions.

The three TMDS channels with DE set to high are used to receive RGB pixel data while the display is on. HSYNC, VSYNC, and user-defined control signals CTL[3:1] are all signals sent over the same three channels. These command signals are received during the display’s blanking period. During blanking, the DE is at a minimum. The following table determines a DVI-compliant system’s TMDS input channel.

TFP401A-Q1 Timekeeping and Information Locking The DVI transmitter provides a clock reference to the TFP401A-Q1 device with a period equal to the pixel time, tpix. Pixel rate is another term for the frequency of this clock. There are 10 bits per 8-bit pixel in the TMDS encoded data on Rx[2:0]; hence the serial bit rate on Rx[2:0] is 10 times the pixel rate. To support a UXGA resolution at 60 hertz, for instance, a pixel rate of 165 MHz is necessary. TMDS employs a serial bit rate of 1.65 Gb/s, or 10 times the pixel rate. There is no guarantee of phase synchronization between the data streams and the input reference clock because this high-speed digital bit stream is transmitted on three distinct channels (or twisted-pair cables) over considerable distances (3-5 meters). Furthermore, there is typically a skew across the three data channels.

To provide stable synchronization with channel-to-channel skew tolerance of up to 1 tpix, the TFP401A-Q1 device employs a 4 oversampling method of the input data streams. Jitter on the clock and data lines, caused by internal and external reflections and noise, is another hallmark of high-speed serial data transmission. The TFP401A-Q1 was developed with a high jitter tolerance in mind. The TFP401A-Q1 device’s input clock is conditioned by a phase-locked loop (PLL) to filter out high-frequency jitter. To pinpoint and synchronize the TMDS data streams (4x oversampling), the PLL generates four 10MHz clock outputs of varying phases. When the display is active, the pixel data is encoded to minimize transitions, and when the display is blank, the control data is encoded to maximize them.

For the receiver to have enough time to synchronize the data when it receives a transition-maximized code, a DVI-compliant transmitter must transmit in the blank for at least 128 tpix. Data-bit boundary detection reliability is ensured by synchronization during blank when the data is transition-maximized. Each of the three input channels has its distinct phase synchronization to the data streams, which is preserved for as long as the link is operational.

Use robust ground planes and connect them using as few vias as possible. With this, current will have a place to go that is both safe and desirable. Each source should have its dedicated power plane, with as much surface area as possible. The power and ground pins of the PanelBus receiver and bypass caps must be connected via a via to the appropriate power or ground plane. To reduce inductance, vias should be as thick and short as technologically possible.

If you have any questions or want to place an order for TFP401AIPZPRQ1, you can contact ICRFQ, China’s leading provider of electrical components.

WhatsApp us