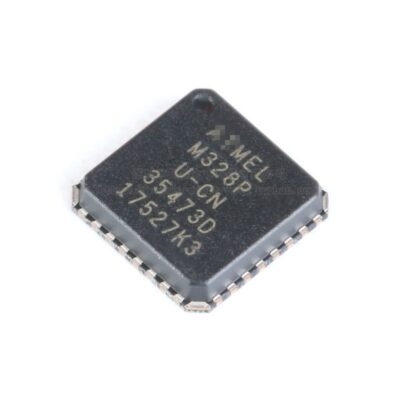

ATMEGA328P-MUR

Part Number: ATMEGA328P-MUR

Manufacturer: Microchip Technology

Description: IC MCU 8BIT 32KB FLASH 32VQFN

Shipped from: Shenzhen/HK Warehouse

Stock Available: Check with us

ICRFQ.com - Electronic Components Distributor in China Since 2003

Part Number: ATMEGA328P-MUR

Manufacturer: Microchip Technology

Description: IC MCU 8BIT 32KB FLASH 32VQFN

Shipped from: Shenzhen/HK Warehouse

Stock Available: Check with us

| Datasheet | |

|---|---|

| Category | Integrated Circuits (ICs) |

| Family | Embedded – Microcontrollers |

| Manufacturer | Atmel |

| Series | AVR? ATmega |

| Packaging | Tape & Reel (TR) |

| Part Status | Active |

| Core Processor | AVR |

| Core Size | 8-Bit |

| Speed | 20MHz |

| Connectivity | I2C, SPI, UART/USART |

| Peripherals | Brown-out Detect/Reset, POR, PWM, WDT |

| Number of I/O | 23 |

| Program Memory Size | 32KB (16K x 16) |

| Program Memory Type | FLASH |

| EEPROM Size | 1K x 8 |

| RAM Size | 2K x 8 |

| Voltage – Supply (Vcc/Vdd) | 1.8 V ~ 5.5 V |

| Data Converters | A/D 8x10b |

| Oscillator Type | Internal |

| Operating Temperature | -40°C ~ 85°C (TA) |

| Package / Case | 32-VFQFN Exposed Pad |

| Supplier Device Package | 32-VQFN (5×5) |

The ATmega ATMEGA328P-MURP microcontroller are built on the AVR® improved RISC architecture and offer a low-power CMOS 8-bit solution for embedded systems. These microcontrollers have the ability to execute instructions in just one clock cycle, resulting in a CPU throughput of up to one million instructions per second (MIPS) per megahertz. This powerful feature allows system designers to optimize performance while maintaining energy efficiency.

The CPU’s principal responsibility is ensuring the system’s software runs without hiccups. Hence, the central processing unit requires memory access, the ability to calculate, management of the peripherals, and interrupt handling.

The AVR employs a Harvard architecture, which features dedicated program, data memory, and buses to increase performance and parallelism. Program memory instructions are executed via single-level pipelining. The next instruction to be executed is acquired from memory ahead of time to begin execution while the current one is still being processed. A clock can be programmed to carry out specific instructions at each tick. In-System-Reprogrammable Flash Memory is used for the software’s main memory. In the fast-access Register File, 32 8-bit general-purpose working registers can be accessed in a single clock cycle.

This permits Arithmetic Logic Unit (ALU) operation in a single cycle. An ALU uses a single clock cycle to read in two Register File inputs, calculate the result, output the result, and then return the result to the Register File. Because three of the 32 registers are 16-bit indirect address registers for the Data Space, we can quickly and precisely compute addresses using just six of the registers. Flash program memory lookup tables can be accessed through one of these address points. The 16-bit X-register, Y-register, and Z-register with new functions will be discussed below. The ALU allows logic and arithmetic operations to be performed between registers or a constant and a register. The ALU is not limited to only performing multi-register operations. Once an arithmetic operation has been completed, the Status Register is modified to reflect the new data.

Conditional and unconditional jump and call instructions, which can directly address the entire address space, provide the program flow. The typical size of an AVR instruction word is 16. A 16- or 32-bit program command is associated with each computer’s memory map address. For software, there are two independent pools of flash memory: the boot and application programs. Separate Lock bits secure both the read and write operations in both memory regions. The SPM instruction that creates the new file in the Application Flash memory sector must be in the Boot Program. The Stack temporarily holds the Program Counter (PC) and return address during interruptions and subroutine calls.

Since the Stack is built within the general data SRAM, its size is limited only by the amount of free and allocated SRAM. Any user-run program performing a Reset must first initialize the SP. The Stack Pointer (SP) can be read from and written to in I/O address space. The data SRAM is easily accessible via the five various addressing modes provided by the AVR design. All AVR memory maps are linear and perfectly regular because of the architecture’s focus on efficiency. The registers used to manage a versatile interrupt module are located in the I/O area, and the Status Register also has a Global Interrupt Enable bit. Each of your system’s interruptions has its unique entry in the Interrupt Vector database.

The Interrupt Vector order determines the priority of the interrupts. A lower Interrupt Vector address indicates a higher priority. Control Registers and other CPU peripherals take up 64 of the available 256 bytes of I/O memory. SPI and other I/O operations. You can either use the address range 0x20:0x5F in the Data Space to gain access to the I/O Memory, or you can access the Register File directly. In addition, the Extended I/O region in SRAM from 0x60 to 0xFF is reserved for use with the ST/STS/STD and LD/LDS/LDD instructions exclusively in the ATmega48A/PA/88A/PA/168A/PA/328/P.

All 32 functioning registers serve a general purpose and are wired directly to the fast AVR ALU. It is possible to perform arithmetic operations between general-purpose registers or between a register and an immediate in a single clock cycle. Three major types of operations can be performed by an ALU: arithmetic, logic, and bit functions. Certain implementations of the design supply a robust multiplier that can handle signed/unsigned multiplication and fractional format. For a complete rundown, check out the “Instruction Set” section.

The Status Register keeps track of the numerical output of the most recent arithmetic instruction. The application can use this information to carry out conditional processes. The Instruction Set Guide states that the status register changes after each ALU operation. This will make the code faster and smaller by reducing the times the dedicated compare instructions need to be used. Upon entering an interrupt routine, the Status Register is not saved and restored automatically. There’s no way around having software manage this.

Temporary data, local variables, and return addresses from interrupts and subroutine calls are all common uses for the Stack. A key aspect of the Stack’s implementation is expanding from more recent to more distant memory locations. The Stack Pointer Register always indicates the top of the stack. The Subroutine and Interrupt Stacks can be found in the data SRAM Stack section, which is pointed to by the Stack Pointer. The Stack Pointer is lowered when the PUSH command is sent. Before calling any subroutines or enabling interrupts, the software must specify the Stack in the data SRAM. For the internal SRAM to function properly, the Stack Pointer must be initialized to point past the beginning of the memory bank.

There are several interrupt sources available in the AVR. There is a dedicated program vector in each interrupt’s memory space and a distinct one for the Reset Vector. The Status Register contains a separate bit for each interrupt that must be written logic one in conjunction with the Global Interrupt Enable bit to enable the interrupt. When bits BLB02 and BLB12 of the Boot Lock register are set, interrupts may be silenced by default, depending on the state of the Program Counter.

Ultimately, the ATmega48A/PA/88A/PA/168A/PA/328/P microcontrollers provide an outstanding balance of power and low power consumption. Their economic power consumption, cutting-edge RISC and Harvard architectures, and adaptable interrupt module make them a great choice for high-performance applications. The microcontrollers’ capabilities can be expanded thanks to built-in capabilities, such as In-System Reprogrammable Flash program memory, EEPROM, internal SRAM, and independent lock bits. If you want to incorporate the ATMEGA328P-MUR or other top-quality electronic components into your project, don’t hesitate to contact ICRFQ. Our team of experts can provide the guidance and support you need to turn your ideas into reality. Let ICRFQ be your trusted partner in your quest for cutting-edge, high-performance power electronics.

WhatsApp us