MPC5200CVR400B

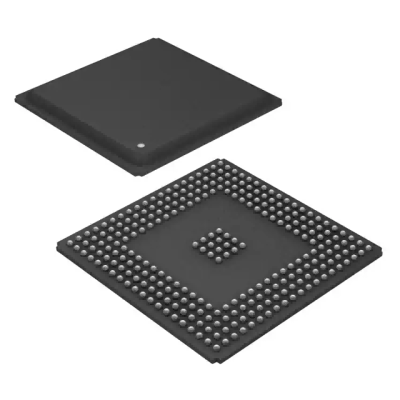

Part Number: MPC5200CVR400B

Manufacturer: NXP Semiconductors

Description: Microprocessors – MPU HABANERO INDUS PBFREE

Shipped from: Shenzhen/HK Warehouse

Stock Available: Check with us

ICRFQ.com - Electronic Components Distributor in China Since 2003

Part Number: MPC5200CVR400B

Manufacturer: NXP Semiconductors

Description: Microprocessors – MPU HABANERO INDUS PBFREE

Shipped from: Shenzhen/HK Warehouse

Stock Available: Check with us

| Datasheet | |

|---|---|

| Category | Integrated Circuits (ICs) |

| Family | Embedded – Microprocessors |

| Manufacturer | Freescale Semiconductor – NXP |

| Series | MPC52xx |

| Packaging | Tray |

| Part Status | Active |

| Core Processor | PowerPC e300 |

| Number of Cores/Bus Width | 1 Core, 32-Bit |

| Speed | 400MHz |

| Co-Processors/DSP | – |

| RAM Controllers | DDR, SDRAM |

| Graphics Acceleration | No |

| Display & Interface Controllers | – |

| Ethernet | 10/100 Mbps (1) |

| SATA | – |

| USB | USB 1.1 (2) |

| Voltage – I/O | 2.5V, 3.3V |

| Operating Temperature | -40°C ~ 85°C (TA) |

| Security Features | – |

| Package / Case | 272-BBGA |

| Supplier Device Package | 272-PBGA (27×27) |

| Additional Interfaces | AC97, CAN, J1850, I2C, I2S, IrDA, PCI, PSC, SPI, UART |

The MPC5200B blends a high-performance MPC603e series e300 core with a wide range of peripheral capabilities targeted at communications and systems integration. The PowerPC® core architecture serves as the basis for the e300 core design. The MPC5200B has a cutting-edge BestComm I/O subsystem that separates routine maintenance of peripheral functions from the embedded e300 core. Six Programmable Serial Controllers (PSC), I2C, J1850, Timers, CAN, SPI, and GPIOs are included in the MPC5200B, and an SDRAM/DDR Memory Controller, a flexible External Bus Interface, PCI Controller, USB, ATA, and Ethernet.

| Technical | |

| Ambient Temperature Range High | 85 °C |

| Core Architecture | PowerPC |

| Data Bus Width | 32 b |

| Frequency | 400 MHz |

| Interface | I2C, SPI, USB |

| Max Frequency | 400 MHz |

| Max Junction Temperature (Tj) | 115 °C |

| Max Operating Temperature | 85 °C |

| Max Supply Voltage | 1.58 V |

| Memory Size | 16 kB |

| Min Operating Temperature | -40 °C |

| Min Supply Voltage | 1.42 V |

| Number of Bits | 32 |

| Number of Cores | 1 |

| Number of Ethernet Channels | 1 |

| Number of I2C Channels | 2 |

| Number of I/Os | 56 |

| Number of PWM Channels | 8 |

| Number of SPI Channels | 6 |

| Number of Timers/Counters | 8 |

| Number of UART Channels | 6 |

| Number of USB Channels | 1 |

| Operating Supply Voltage | 1.5 V |

| Peripherals | DMA, POR |

| RAM Size | 16 kB |

| Schedule B | 8542310000 |

| Termination | SMD/SMT |

| Physical | |

| Case/Package | BGA |

| Contact Plating | Copper, Silver, Tin |

| Mount | Surface Mount |

| Number of Pins | 272 |

| Weight | 2.545192 g |

| Dimensions | |

| Height | 2.65 mm |

| Compliance | |

| Lead-Free | Lead-Free |

| Radiation Hardening | No |

| REACH SVHC | No SVHC |

Memory protection is provided by a memory protection unit (MPU), a piece of computer hardware. Typically, it is implemented as a central processing unit (CPU) component. A simplified version of the memory management unit (MMU), the memory protection unit (MPU), only supports memory protection. It is typically used in low-power CPUs because they merely need memory protection and don’t require advanced features like virtual memory management.

The MPU gives privileged software the ability to establish memory areas and give each one a unique set of memory properties and access permissions. The number of supported memory regions varies depending on how the CPU is implemented. The MPU can support up to 16 regions on ARMv8-M CPUs. The memory attributes define the ordering, merging, caching, and buffering actions of these regions. If accessible, cache properties can be exported for use by system caches and used by internal caches.

The MPU keeps track of all transactions, including data accesses and instruction fetches from the processor. The MPU may raise a fault exception if an access violation is discovered. Thanks to memory protection, a process cannot access memory that has not been allotted to it. Doing this prevents a process’s defect or malware from other processes and the operating system as a whole.

The MPU prevents malicious processes from bad system memory and user memory regions. Permissions for several embedded operating systems at the privileged and unprivileged access levels (OS).

Thanks for reading. If you like this article, please explore the rest of our website for more great content like this one and learn more. If you have any questions about this article, please leave them in the comment section below, and we will do our best to respond to them.

If you need information or want to order MPC5200B, contact us here at ICRFQ, your leading electronic components in china, and we will ensure you get the best product at the best price.

WhatsApp us