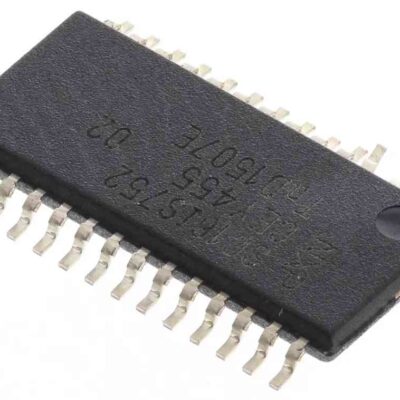

SC16IS752IPW

Part Number: SC16IS752IPW

Manufacturer: NXP USA Inc.

Description: IC UART DUAL 12C/SPI 28TSSOP

Shipped from: Shenzhen/HK Warehouse

Stock Available: Check with us

ICRFQ.com - Electronic Components Distributor in China Since 2003

Part Number: SC16IS752IPW

Manufacturer: NXP USA Inc.

Description: IC UART DUAL 12C/SPI 28TSSOP

Shipped from: Shenzhen/HK Warehouse

Stock Available: Check with us

| Datasheet | |

|---|---|

| Category | Integrated Circuits (ICs) |

| Family | Interface – Controllers |

| Manufacturer | NXP Semiconductors |

| Series | – |

| Packaging | Tube |

| Part Status | Active |

| Protocol | RS232, RS485 |

| Function | Controller |

| Interface | I2C, SPI, UART |

| Standards | – |

| Voltage – Supply | 2.5V, 3.3V |

| Current – Supply | 2mA |

| Operating Temperature | -40°C ~ 95°C |

| Package / Case | 28-TSSOP (0.173″, 4.40mm Width) |

| Supplier Device Package | 28-TSSOP |

The SC16IS752IPW connects an I2C-bus or SPI bus to a high-performance dual-channel UART that can handle data rates of up to 5 Mbit/s, low operating and resting current, and 8 additional programmable I/O pins for the application. The device is perfectly suited for hand-held, battery-operated applications because it is available in relatively compact HVQFN32 and TSSOP28 packages. This fully bidirectional device offers flawless protocol translation from I2C-bus/SPI to RS-232/RS-485.

The SC16IS762 differs from the SC16IS752 in that it supports IrDA SIR up to 1.152 Mbit/s and SPI clock rates of up to 15 Mbit/s as opposed to just 4 Mbit/s as provided by the SC16IS752. The SC16IS762 is functionally and electrically identical to the SC16IS752 in all other respects. The internal register set of the SC16IS752IPW is backward compatible with the commonly used and favored 16C450. Writing new software or porting existing software from another platform is simple. Other cutting-edge features offered by the SC16IS752/SC16IS762 include automatic hardware and software flow control, automatic RS-485 compatibility, and software reset. As a result, regardless of the hardware reset signal, the software can reset the UART at any time.

The components of hardware flow control are Auto-CTS and Auto-RTS (see Figure 4). Programming EFR enables/disables Auto-CTS and Auto-RTS independently[7:6]. Before the UART transmits data using Auto-CTS, CTS must be engaged. When the RX FIFO is sufficiently filled, Auto-RTS deactivates the RTS output and only activates it again when there is sufficient space in the FIFO to receive data. The Transmission Control Register’s (TCR) halt and resume trigger levels specify the levels at which RTS is enabled or deactivated.

If the TCR bits are cleared, TCR is replaced with customizable trigger levels in FCR. When both Auto-CTS and Auto-RTS are enabled, data transfer only happens when the receiver FIFO is empty, and RTS is connected to CTS. Overrun faults are therefore removed during hardware flow control. If overrun errors are not enabled, they happen when the receive FIFO servicing latency is longer than the transmit data rate.

The RS-485 mode is enabled by setting EFCR bit 0 to 0. (multidrop or 9-bit mode). For the addressed “slave” stations, a “master” station sends an address character followed by data characters. If an address character (with a parity bit of 1) is detected in the incoming data by the slave stations, they evaluate it and interrupt the controller. The software would need to turn off the hardware flow control mechanism to use the auto RS-485 RTS mode..

Bit 0 of the EFCR’s 9-bit mode is enabled, but Special Character Detect is disabled (EFR bit 5). To identify address bytes, the receiver is configured to Force Parity 0 (LCR[5:3] = 111). The receiver is initially turned off and rejects all data bytes (parity bit = 0) until an address byte (parity bit = 1) is received. The UART will set the parity fault due to this address byte. This address byte will be placed in the RX FIFO simultaneously as the UART generates a line status interrupt (IER bit 2 must be set to “1” now). The controller must decide whether to activate the receiver after examining the byte; if the address byte addresses the receiver’s ID address, the receiver should be enabled; otherwise, the receiver should not be enabled.

If the controller enables the receiver, it will continue to receive data until the controller disables it after receiving a full message from the “master” station. The receiver will produce a parity error when it receives another address byte if the controller does not turn it off after receiving a message from the “master” station. If the address byte does not match the receiver’s ID address, the controller can disable the receiver. The controller won’t take any further action; the receiver will receive the succeeding data if the address byte refers to the “slave” ID address.

The receiver will attempt to locate an address byte that matches the character that was programmed in XOFF2 if Special Character Detect is enabled (EFR[5] is set, and XOFF2 contains the address byte). The receiver will delete the data if the received byte is a data or address byte that does not match the character programmed in XOFF2. If the receiver isn’t already activated, it will be when an address byte matching the XOFF2 character is received. The address character and parity bit are then pushed into the RX FIFO (in place of the parity error bit).

Moreover, the receiver produces a line status interrupt (IER bit 2 must be set to 1 now). After receiving a message from the “master” station, the receiver will continue to receive data from that station until it is disabled by the controller. The receiver will be instantly disabled and the address byte disregarded if another address byte is received but does not match the XOFF2 character. The receiver will place this byte and the parity bit in the parity error bit in the RX FIFO if the address byte matches the XOFF2 character (LSR[2]).

NXP Semiconductors makes the flexible SC16IS752IPW UART IC with two channels. It lets an I2C/SPI microcontroller and two asynchronous serial communication ports talk in both directions. The IC supports IrDA SIR up to 115.2 kbps and has a programmable baud rate of up to 5 Mbps, auto RTS/CTS and XON/XOFF flow control, and auto RTS/CTS and XON/XOFF flow control. It can be used for various things, like industrial automation, medical equipment, point-of-sale terminals, security systems, data acquisition systems, gaming machines, and communication systems.

If you want to buy the SC16IS752IPW or any other electronic part, you might want to talk to ICRFQ, China’s best electronic parts distributor. We’re a great choice for your technology needs because we sell high-quality items at reasonable prices. Please get in touch with us right away if you want to know more.

WhatsApp us